# SN54190, SN54191, SN54LS190, SN54LS191, SN74190, SN74191, SN74LS190, SN74LS191 SYNCHRONOUS UP/DOWN COUNTERS WITH DOWN/UP MODE CONTROL

SDLS072 - DECEMBER 1972 - REVISED MARCH 1988

- Counts 8-4-2-1 BCD or Binary

- Single Down/Up Count Control Line

- Count Enable Control Input

- Ripple Clock Output for Cascading

- Asynchronously Presettable with Load Control

- Parallel Outputs

- Cascadable for n-Bit Applications

|               |                    | TYPICAL   |             |

|---------------|--------------------|-----------|-------------|

|               | AVERAGE            | MAXIMUM   | TYPICAL     |

| TYPE          | <b>PROPAGATION</b> | CLOCK     | POWER       |

|               | DELAY              | FREQUENCY | DISSIPATION |

| 190,191       | 20 ns              | 25MHz     | 325mW       |

| 'LS190,'LS191 | 20 ns              | 25MHz     | 100mW       |

#### description

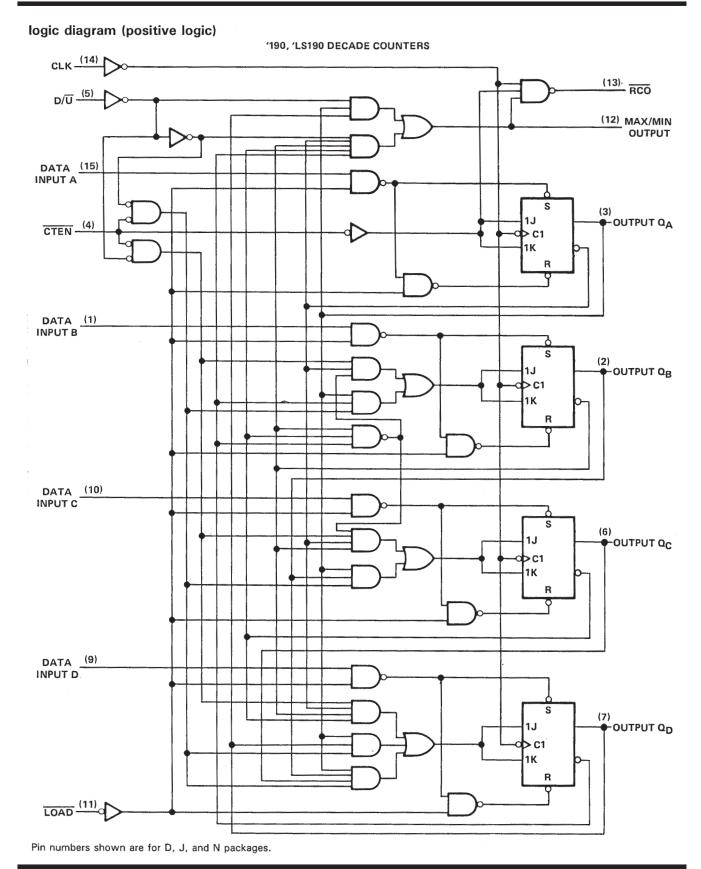

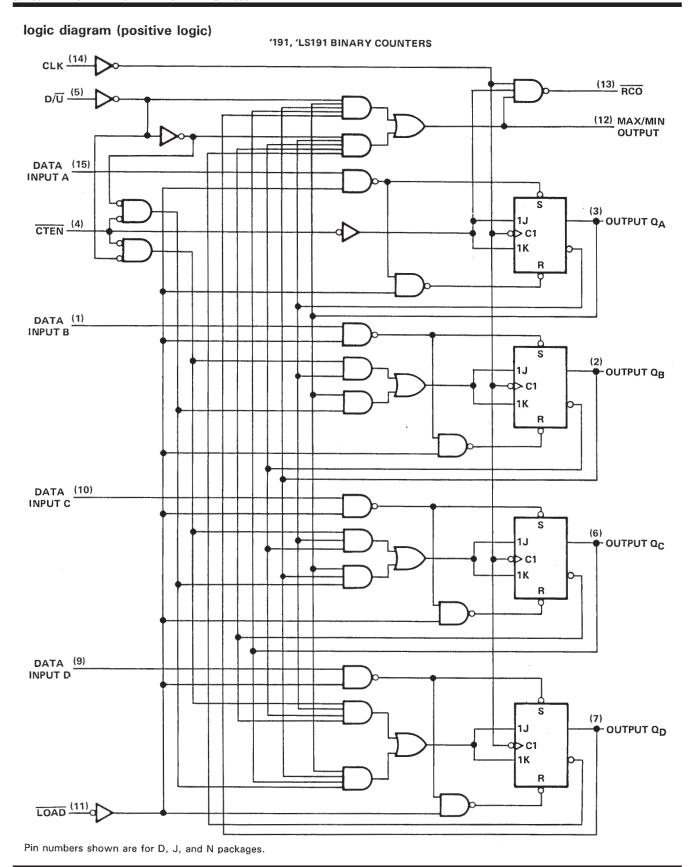

The '190, 'LS190, '191, and 'LS191 are synchronous, reversible up/down counters having a complexity of 58 equivalent gates. The '191 and 'LS191 are 4-bit binary counters and the '190 and 'LS190 are BCD counters. Synchronous operation is provided by having all flipflops clocked simultaneously so that the outputs change coincident with each other when so instructed by the steering logic. This mode of operation eliminates the output counting spikes normally associated with asynchronous (ripple clock) counters.

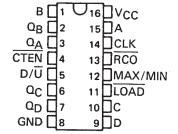

SN54190, SN54191, SN54LS190, SN54LS191 . . . J PACKAGE SN74190, SN74191 . . . N PACKAGE SN74LS190, SN74LS191 . . . D OR N PACKAGE (TOP VIEW)

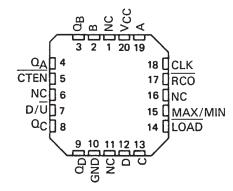

SN54LS190, SN54LS191 . . . FK PACKAGE (TOP VIEW)

NC - No internal connection

The outputs of the four master-slave flip-flops are triggered on a low-to-high transition of the clock input if the enable input is low. A high at the enable input inhibits counting. Level changes at the enable input should be made only when the clock input is high. The direction of the count is determined by the level of the down/up input. When low, the counter count up and when high, it counts down. A false clock may occur if the down/up input changes while the clock is low. A false ripple carry may occur if both the clock and enable are low and the down/up input is high during a load pulse.

These counters are fully programmable; that is, the outputs may be preset to either level by placing a low on the load input and entering the desired data at the data inputs. The output will change to agree with the data inputs independently of the level of the clock input. This feature allows the counters to be used as modulo-N dividers by simply modifying the count length with the preset inputs.

The clock, down/up, and load inputs are buffered to lower the drive requirement which significantly reduces the number of clock drivers, etc., required for long parallel words.

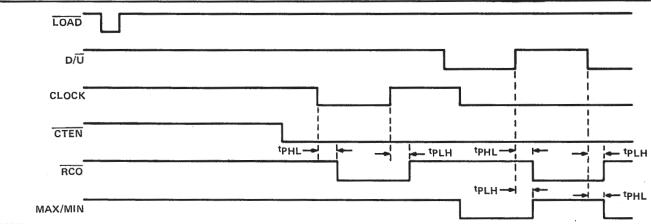

Two outputs have been made available to perform the cascading function: ripple clock and maximum/minimum count. The latter output produces a high-level output pulse with a duration approximately equal to one complete cycle of the clock when the counter overflows or underflows. The ripple clock output produces a low-level output pulse equal in width to the low-level portion of the clock input when an overflow or underflow condition exists. The counters can be easily cascaded by feeding the ripple clock output to the enable input of the succeeding counter if parallel clocking is used, or to the clock input if parallel enabling is used. The maximum/minimum count output can be used to accomplish look-ahead for high-speed operation.

Series 54' and 54LS' are characterized for operation over the full military temperature range of -55°C to 125°C; Series 74' and 74LS' are characterized for operation from 0°C to 70°C.

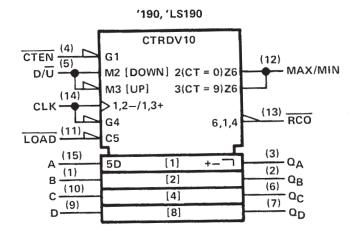

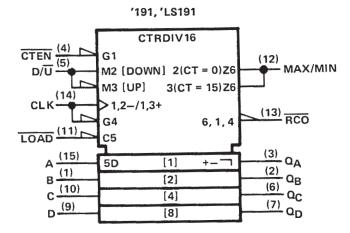

# logic symbols†

<sup>&</sup>lt;sup>†</sup> These symbols are accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12. Pin numbers shown are for D, J, and N packages.

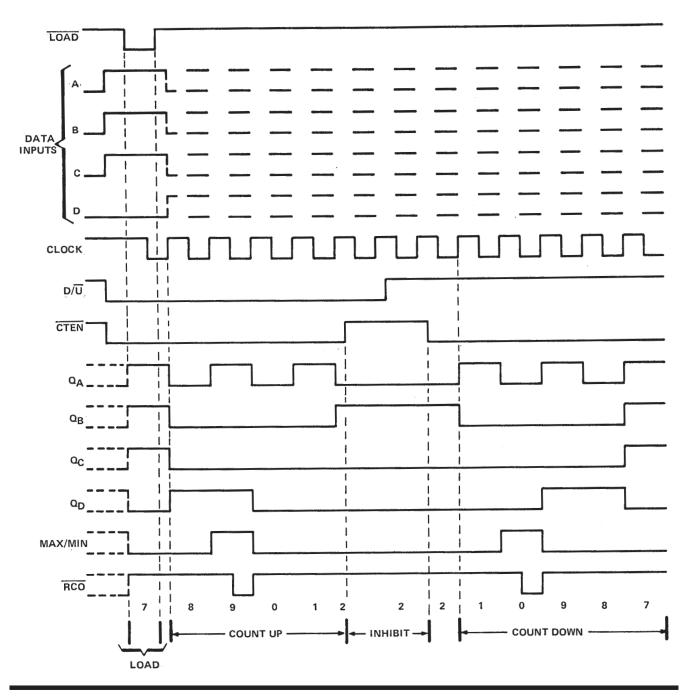

## '190, 'LS190 DECADE COUNTERS

### typical load, count, and inhibit sequences

Illustrated below is the following sequence:

- 1. Load (preset) to BCD seven.

- 2. Count up to eight, nine (maximum), zero, one, and two.

- 3. Inhibit.

- 4. Count down to one, zero (minimum), nine, eight, and seven.

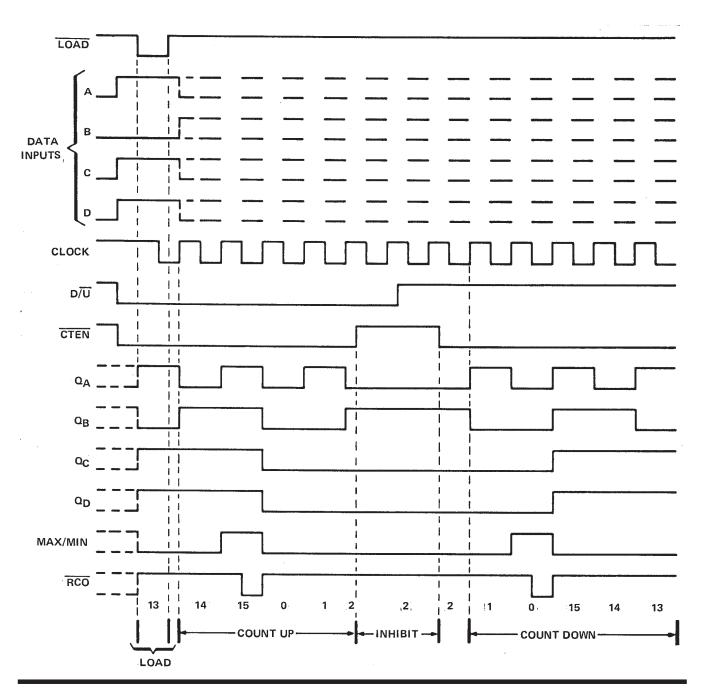

# '191, 'LS191 BINARY COUNTERS

## pical load, count, and inhibit sequences

Illustrated below is the following sequence:

- 1. Load (preset) to binary thirteen.

- 2. Count up to fourteen, fifteen (maximum), zero, one, and two.

- 3. Inhihit

- 4. Count down to one, zero (minimum), fifteen, fourteen, and thirteen.

# SN54190, SN54191, SN54LS190, SN54LS191, SN74190, SN74191, SN74LS190, SN74LS191 SYNCHRONOUS UP/DOWN COUNTERS WITH DOWN/UP MODE CONTROL

SDLS072 - DECEMBER 1972 - REVISED MARCH 1988

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, V <sub>CC</sub> (see Note 1)                  | V |

|---------------------------------------------------------------|---|

| Input voltage: SN54', SN74' Circuits                          | V |

| SN54LS', SN74LS' Circuits                                     |   |

| Operating free-air temperature range: SN54', SN54LS' Circuits | С |

| SN74', SN74LS' Circuits                                       | С |

| Storage temperature range                                     | С |

NOTE 1: Voltage values are with respect to network ground terminal.

#### recommended operating conditions

|                 |                    |                                        | SN54 | 190, SN | 154191 | SN74190, SN74191 |     |       | UNIT  |  |

|-----------------|--------------------|----------------------------------------|------|---------|--------|------------------|-----|-------|-------|--|

|                 |                    |                                        | MIN  | NOM     | MAX    | MIN              | NOM | MAX   | 0.4.1 |  |

| Vcc             | Supply voltage     |                                        | 4.5  | 5       | 5.5    | 4.75             | 5   | 5.25  | V     |  |

| ЮН              | High-level output  | current                                |      |         | - 0.8  |                  |     | - 0.8 | mA    |  |

| loL             | Low-level output   | current                                |      |         | 16     |                  |     | 16    | mA    |  |

| fclock          | Input clock frequ  | 0                                      |      | 20      | 0      |                  | 20  | MHz   |       |  |

| tw(clock)       | Width of clock in  | out pulse                              | 25   |         |        | 25               |     |       | ns    |  |

| tw(load)        | Width of load inp  | ut pulse                               | 35   |         |        | 35               |     |       | ns    |  |

|                 | Setup time         | Data, high or low (See Figure 1 and 2) | 20   |         |        | 20               |     |       | ns    |  |

| t <sub>su</sub> | Setup time         | Load inactive state                    | 20   |         |        | 20               |     |       | 113   |  |

| thold           | Data hold time     |                                        | 0    |         |        | 0                |     |       | ns    |  |

| TA              | Operating free-air | Operating free-air temperature         |      |         |        | 0                |     | 70    | °C    |  |

## electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                 | PARAMETER                                           | TEST CONDITIONS†                                                                                    | SN54 | 190, SN | 54191 | SN74 | 190, SN | 74191 |      |

|-----------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|---------|-------|------|---------|-------|------|

|                 | PARAMETER                                           | TEST CONDITIONS:                                                                                    | MIN  | TYP‡    | MAX   | MIN  | TYP‡    | MAX   | UNIT |

| $V_{1H}$        | High-level input voltage                            | V <sub>CC</sub> = MIN                                                                               | 2    |         |       | 2    |         |       | V.   |

| ۷۱۲             | Low-level input voltage                             | V <sub>CC</sub> = MIN                                                                               |      |         | 0.8   |      |         | 0.8   | ٧    |

| $v_{1K}$        | Input clamp voltage                                 | V <sub>CC</sub> = MIN, I <sub>1</sub> = -12 mA                                                      |      |         | -1.5  |      |         | -1.5  | V    |

| V <sub>OH</sub> | High-level output voltage                           | V <sub>CC</sub> = MIN, V <sub>IH</sub> = 2 V,<br>V <sub>IL</sub> = 0.8 V, I <sub>OH</sub> = -0.8 mA | 2.4  | 3.4     |       | 2.4  | 3.4     |       | V    |

| VOL             | Low-level output voltage                            | V <sub>CC</sub> = MIN, V <sub>IH</sub> = 2 V,<br>V <sub>IL</sub> = 0.8 V, I <sub>OL</sub> = 16 mA   |      | 0.2     | 0.4   |      | 0.2     | 0.4   | V    |

| l <sub>1</sub>  | High-level input current at maximum input voltage   | V <sub>CC</sub> = MAX, V <sub>I</sub> = 5.5 V                                                       |      |         | 1     |      |         | 1     | mA   |

| ΊΗ              | High-level input current at any input except enable |                                                                                                     |      | -       | 40    |      |         | 40    | μА   |

| ΉΗ              | High-level input current at enable input            | V <sub>CC</sub> = MAX, V <sub>I</sub> = 2.4 V                                                       |      |         | 120   |      |         | 120   | μΑ   |

| IIL             | Low-level input current at any input except enable  | VCC = MAX, VI = 0.4 V                                                                               |      |         | -1.6  |      |         | -1.6  | mA   |

| IIL             | Low-level input current at enable input             | VCC - WAX, V - 0.4 V                                                                                |      |         | -4.8  |      |         | -4.8  | mA   |

| los             | Short-circuit output current§                       | V <sub>CC</sub> = MAX                                                                               | -20  |         | -65   | -18  |         | -65   | mA   |

| ICC             | Supply current                                      | V <sub>CC</sub> = MAX, See Note 2                                                                   |      | 65      | 99    |      | 65      | 105   | mA   |

$<sup>^\</sup>dagger$  For conditions shown as MAX or MIN, use appropriate value specified under recommended operating conditions.

NOTE 2:  $I_{\mbox{\footnotesize{CC}}}$  is measured with all inputs grounded and all outputs open.

<sup>‡</sup>All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25 ^{\circ} \text{C}$ .

$<sup>\</sup>S$  Not more than one output should be shorted at a time.

# SN54190, SN54191, SN74190, SN74191 SYNCHRONOUS UP/DOWN COUNTERS WITH DOWN/UP MODE CONTROL

SDLS072 - DECEMBER 1972 - REVISED MARCH 1988

# switching characteristics, $V_{CC} = 5 \text{ V}$ , $T_A = 25^{\circ}\text{C}$

| DADAMETEC+       | FROM            | то                                                                                                   | 7507 001/01/7/01/7                     |     | 190, '1 | 91  |       |

|------------------|-----------------|------------------------------------------------------------------------------------------------------|----------------------------------------|-----|---------|-----|-------|

| PARAMETER†       | (INPUT)         | (OUTPUT)                                                                                             | TEST CONDITIONS                        | MIN | TYP     | MAX | UNIT  |

| f <sub>max</sub> |                 |                                                                                                      | •                                      | 20  | 25      |     | MHz   |

| <sup>t</sup> PLH | Load            | $Q_A, Q_B, Q_C, Q_D$ $Q_A, Q_B, Q_C, Q_D$ $\overline{RCO}$ $Q_A, Q_B, Q_C, Q_D$ $\overline{Max/Min}$ |                                        |     | 22      | 33  | ns    |

| <sup>t</sup> PHL | Load            |                                                                                                      |                                        |     | 33      | 50  | ] "15 |

| <sup>t</sup> PLH | Data A, B, C, D |                                                                                                      | 1                                      |     | 14      | 22  | ns    |

| tPHL t           |                 |                                                                                                      | $C_L = 15  pF$ , $R_L = 400  \Omega$ , |     | 35      | 50  | 115   |

| <sup>t</sup> PLH |                 |                                                                                                      |                                        |     | 13      | 20  | ns    |

| <sup>t</sup> PHL | J OLIK          |                                                                                                      | See Figures 1 and 3 thru 7             |     | 16      | 24  | ] "15 |

| <sup>t</sup> PLH | CLK             |                                                                                                      |                                        |     | 16      | 24  | ns ns |

| t <sub>PHL</sub> |                 |                                                                                                      |                                        |     | 24      | 36  |       |

| <sup>t</sup> PLH | CLK             |                                                                                                      |                                        |     | 28      | 42  |       |

| <sup>t</sup> PHL | CLK             | IVIQA/IVIIII                                                                                         |                                        |     | 37      | 52  |       |

| <sup>t</sup> PLH | D/Ū             | RCO                                                                                                  | ]                                      |     | 30      | 45  | ns    |

| <sup>t</sup> PHL | ]               | NCO .                                                                                                |                                        |     | 30      | 45  | IIIS  |

| <sup>t</sup> PLH | D/Ū             | Max/Min                                                                                              |                                        |     | 21      | 33  |       |

| <sup>t</sup> PHL | ] 5/0           | IVIGA/IVIIII                                                                                         |                                        |     | 22      | 33  | ns    |

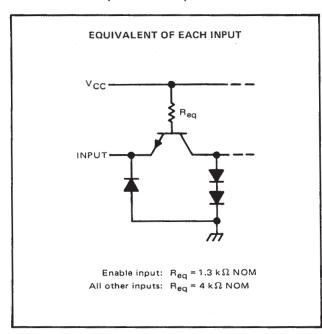

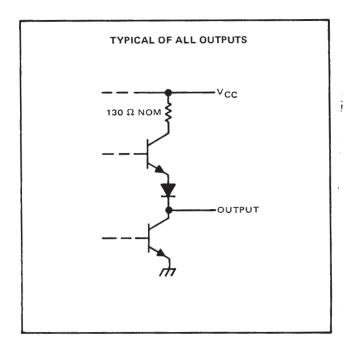

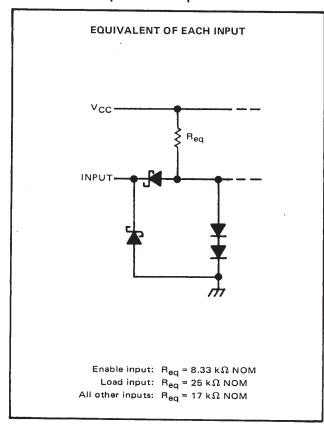

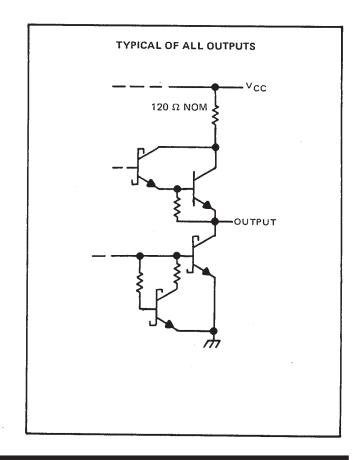

#### schematics of inputs and outputs

$<sup>^{\</sup>dagger}$  f<sub>max</sub> = maximum clock frequency tpLH = propagation delay time, low-to-high-level output

tpHL ≡ propagation delay time, high-to-low-level output

# SN54LS190, SN54LS191, SN74LS190, SN74LS191 SYNCHRONOUS UP/DOWN COUNTERS WITH DOWN/UP MODE CONTROL

SDLS072 - DECEMBER 1972 - REVISED MARCH 1988

#### recommended operating conditions

|                     |                                       |      | SN54LS | 190   | S    | N74LS1 | 90    |      |

|---------------------|---------------------------------------|------|--------|-------|------|--------|-------|------|

|                     |                                       |      | SN54LS | 191   | S    | N74LS1 | 91    | UNIT |

|                     |                                       | MIN  | MOM    | MAX   | MIN  | NOM    | MAX   |      |

| Vcc                 | Supply voltage                        | 4.5  | 5      | 5.5   | 4.75 | 5      | 5.25  | V    |

| ЮН                  | High-level output current             |      |        | - 0.4 |      |        | - 0.4 | mA   |

| loL                 | Low-level output current              |      |        | 4     |      |        | 8     | mA   |

| fclock              | Clock frequency                       | . (  | )      | 20    | 0    |        | 20    | MHz  |

| tw(clock)           | Width of clock input pulse            | 25   | ;      |       | 25   |        |       | ns   |

| tw(load)            | Width of load input pulse             | 35   | 5      |       | 35   |        |       | ns   |

| t <sub>su</sub>     | Data setup time (See Figures 1 and 2) | 20   | )      |       | 20   |        |       | ns   |

| t <sub>su</sub>     | Load inactive state setup time        | 30   | )      |       | 30   |        |       | ns   |

| t <sub>h</sub>      | Data hold time                        |      | 5      |       | 5    |        |       | ns   |

| th                  | Enable hold time                      | (    | ) ,    |       | 0    |        |       | ns   |

| <sup>t</sup> enable | Count enable time (see Note 3)        | 40   | )      |       | 40   |        |       | ns   |

| TA                  | Operating free-air temperature        | - 55 | 5      | 125   | 0    |        | 70    | °c   |

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                 | PARAMETER               |         | TEST CONDITIONS <sup>†</sup>                                     |                                                     |                        | SN54LS190<br>SN54LS191 |      |      | SN74LS190<br>SN74LS191 |              |      | UNIT  |

|-----------------|-------------------------|---------|------------------------------------------------------------------|-----------------------------------------------------|------------------------|------------------------|------|------|------------------------|--------------|------|-------|

|                 |                         |         |                                                                  |                                                     |                        | MIN                    | TYP‡ | MAX  | MIN                    | TYP‡         | MAX  |       |

| VIH             | High-level input voltag | e       |                                                                  |                                                     |                        | 2                      |      |      | 2                      |              |      | ٧     |

| VIL             | Low-level input voltag  | е       |                                                                  |                                                     |                        |                        |      | 0.7  |                        |              | 0.8  | ٧     |

| VIK             | Input clamp voltage     |         | V <sub>CC</sub> = MIN,                                           | I <sub>1</sub> = -18 mA                             |                        |                        |      | -1.5 |                        |              | -1.5 | ٧     |

| V <sub>OH</sub> | High-level output volta | age     | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = V <sub>IL</sub> max, | V <sub>1H</sub> = 2 V,<br>I <sub>OH</sub> = -400 μA |                        | 2.5                    | 3.4  |      | 2.7                    | 3.4          |      | ٧     |

| VOL             | Low-level output volta  | ige     | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = V <sub>IL</sub> max  | V <sub>1H</sub> = 2 V,                              | I <sub>OL</sub> = 4 mA |                        | 0.25 | 0.4  |                        | 0.25<br>0.35 | 0.4  | 1 V 1 |

| l <sub>l</sub>  | High-level input        | Enable  | Vcc = MAX,                                                       | V1 = 7 V                                            |                        |                        |      | 0.3  |                        |              | 0.3  |       |

| ''              | input voltage           | Others  | VCC - WAX,                                                       | V   - / V                                           |                        |                        |      | 0.1  |                        |              | 0.1  | mA    |

| ļ,              | High-level              | Enable  |                                                                  | V = 0.7.V                                           |                        |                        |      | 60   |                        |              | 60   |       |

| ин              | input current           | Others  | V <sub>CC</sub> = MAX,                                           | V   = 2.7 V                                         | V <sub>I</sub> = 2.7 V |                        |      | 20   |                        |              | 20   | μΑ    |

| Lu              | Low-level               | Enable  | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\                           | V. = 0.4.V                                          |                        |                        |      | -1.2 |                        |              | -1.2 | A     |

| IIL.            | input current           | Others  | V <sub>CC</sub> = MAX,                                           | V   - 0.4 V                                         | V <sub>I</sub> = 0.4 V |                        |      | -0.4 |                        |              | -0.4 | mA    |

| los             | Short-circuit output c  | urrent§ | V <sub>CC</sub> = MAX,                                           |                                                     |                        | -20                    |      | -100 | -20                    |              | -100 | mA    |

| 1cc             | Supply current          |         | V <sub>CC</sub> = MAX,                                           | See Note 2                                          |                        |                        | 20   | 35   |                        | 20           | 35   | mA    |

<sup>&</sup>lt;sup>†</sup>For conditions shown as MAX or MIN, use appropriate value specified under recommended operating conditions for the applicable device type.

$<sup>\</sup>ddagger$ AII typical values are at  $V_{CC}$  = 5 V,  $T_A$  = 25°C.

<sup>§</sup>Not more than one output should be shorted at a time, and duration of the short-circuit should not exceed one second.

NOTES: 2. ICC is measured with all inputs grounded and all outputs open.

Minimum count enable time is the interval immediately preceding the rising edge of the clock pulse during which interval the count enable input must be low to ensure counting.

# SN54LS190, SN54LS191, SN74LS190, SN74LS191 SYNCHRONOUS UP/DOWN COUNTERS WITH DOWN/UP MODE CONTROL

SDLS072 - DECEMBER 1972 - REVISED MARCH 1988

# switching characteristics, $V_{CC} = 5 \text{ V}$ , $T_A = 25^{\circ}\text{C}$

| PARAMETER†       | FROM            | то                                                                |                                                | 'LS | S191 | LINIT |      |

|------------------|-----------------|-------------------------------------------------------------------|------------------------------------------------|-----|------|-------|------|

| PARAIVIE I ER    | (INPUT)         | (OUTPUT)                                                          | TEST CONDITIONS                                | MIN | TYP  | MAX   | UNIT |

| f <sub>max</sub> |                 |                                                                   |                                                | 20  | 25   |       | MHz  |

| tPLH.            | Load            | 0. 0- 0- 0-                                                       |                                                |     | 22   | 33    |      |

| tPHL             | Load            | $\Omega_A, \Omega_B, \Omega_C, \Omega_D$                          |                                                |     | 33   | 50    | ns   |

| t <sub>PLH</sub> | Data A, B, C, D | α <sub>A</sub> , α <sub>B</sub> , α <sub>C</sub> , α <sub>D</sub> | 7                                              |     | 20   | 32    | 1    |

| <sup>t</sup> PHL | Data A, B, C, D |                                                                   |                                                |     | 27   | 40    | ns   |

| <sup>t</sup> PLH | CLK             |                                                                   | C <sub>L</sub> = 15 pF, R <sub>L</sub> = 2 kΩ, |     | 13   | 20    |      |

| <sup>t</sup> PHL |                 |                                                                   | See Figures 1 and 3 thru 7                     |     | 16   | 24    | ns   |

| <sup>t</sup> PLH | CLK .           | 0. 0- 0- 0-                                                       | Jee rigules raild 5 tillu 7                    |     | 16   | 24    |      |

| <sup>t</sup> PHL | CLK             | $Q_A, Q_B, Q_C, Q_D$                                              |                                                |     | 24   | 36    | ns   |

| tPLH             | OLK.            | Max/Min                                                           |                                                |     | 28   | 42    | ns   |

| <sup>t</sup> PHL | CLK             |                                                                   |                                                |     | 37   | 52    |      |

| <sup>t</sup> PLH | 5/5             |                                                                   |                                                |     | 30   | 45    |      |

| <sup>t</sup> PHL | D/Ū             | RCO                                                               |                                                |     | 30   | 45    | กร   |

| <sup>t</sup> PLH |                 | Max/Min                                                           | 7                                              |     | 21   | 33    |      |

| <sup>t</sup> PHL | D/Ū             | IVIdX/IVIII)                                                      |                                                |     | 22   | 33    | ns   |

| tpLH_            |                 |                                                                   |                                                |     | 21   | 33    |      |

| <sup>†</sup> PHL | CTEN            | RCO                                                               |                                                |     | 22   | 33    | ns   |

† f<sub>max</sub> ≡ maximum clock frequency tp<sub>LH</sub> ≡ propagation delay time, low-to-high-level output tp<sub>HL</sub> ≡ propagation delay time, high-to-low-level output

### schematics of inputs and outputs

#### PARAMETER MEASUREMENT INFORMATION

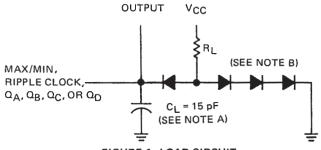

FIGURE 1-LOAD CIRCUIT FOR SWITCHING TIME MEASUREMENT

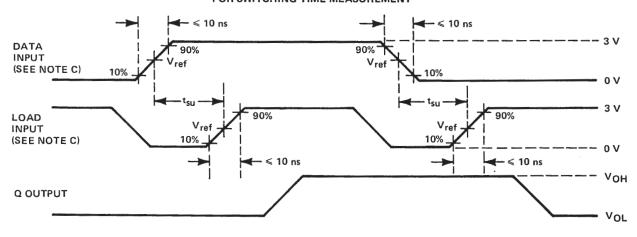

#### FIGUTE 2-DATA SETUP TIME VOLTAGE WAVEFORMS

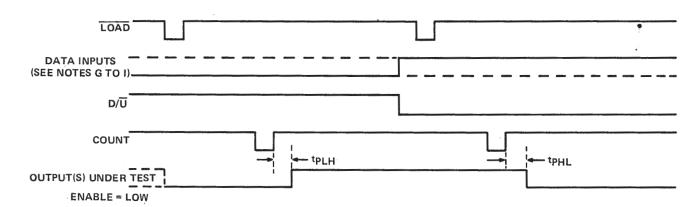

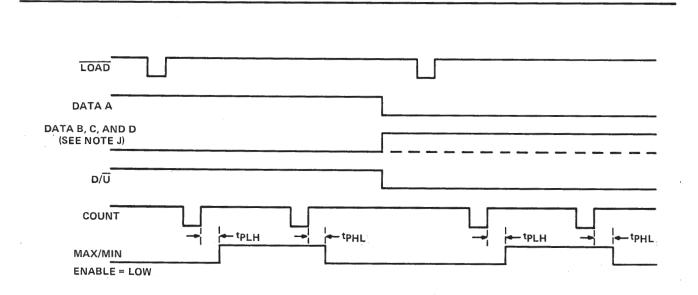

See waveform sequences in figures 4 through 7 for propagation times from a specific input to a specific output. For simplication, pulse rise times, reference levels, etc., have not been shown in figures 4 through 7.

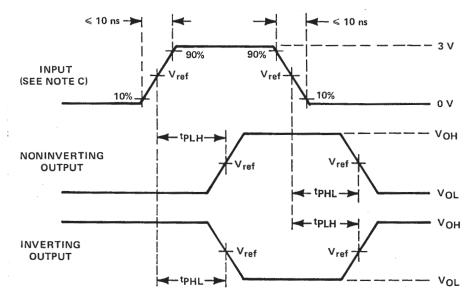

#### FIGURE 3-GENERAL VOLTAGE WAVEFORMS FOR PROPAGATION TIMES

NOTES: A.  $C_L$  includes probe and jig capacitance.

- B. All diodes are 1N3064 or equivalent.

- C. The input pulses are supplied by generators having the following characteristics:  $Z_{out} = 50 \Omega$ , duty cycle  $\leq 50\%$ , PRR  $\leq 1$  MHz.

- D.  $V_{ref} = 1.5 \text{ V}$  for '190 and '191; 1.3 V for 'LS190 and 'LS191.

SDLS072 - DECEMBER 1972 - REVISED MARCH 1988

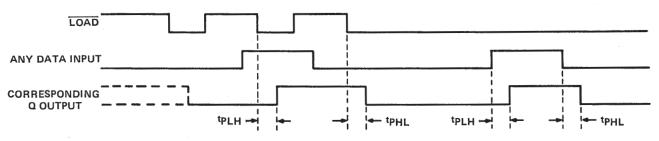

NOTE E: Conditions on other inputs are irrelevant.

FIGURE 4-LOAD TO OUTPUT AND DATA TO OUTPUT

NOTE F: All data inputs are low.

FIGURE 5-ENABLE TO RIPPLE CLOCK, CLOCK TO RIPPLE CLOCK, DOWN/UP TO RIPPLE CLOCK, AND DOWN/UP TO MAX/MIN

#### PARAMETER MEASUREMENT INFORMATION (continued)

switching characteristics (continued)

- NOTES: G. To test Q<sub>A</sub>, Q<sub>B</sub>, and Q<sub>C</sub> outputs of '190 and 'LS190: Data inputs A, B, and C are shown by the solid line. Data input D is shown by the dashed line.

- H. To test Q<sub>D</sub> output of '190 and 'LS190: Data inputs A and D are shown by the solid line. Data inputs B and C are held at the low logic level.

- I. To test  $Q_A$ ,  $Q_B$ ,  $Q_C$ , and  $Q_D$  outputs of '191 and 'LS191: All four data inputs are shown by the solid line.

#### FIGURE 6-CLOCK TO OUTPUT

NOTE J: Data inputs B and C are shown by the dashed line for the '190 and 'LS190 and the solid line for the '191 and 'LS191: Data input D is shown by the solid line for both devices.

FIGURE 7-CLOCK TO MAX/MIN

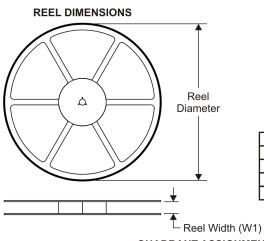

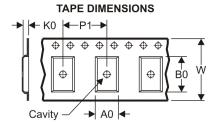

### TAPE AND REEL INFORMATION

| _   |    |                                                           |

|-----|----|-----------------------------------------------------------|

| I   |    | Dimension designed to accommodate the component width     |

| I   | B0 | Dimension designed to accommodate the component length    |

|     | K0 | Dimension designed to accommodate the component thickness |

|     | W  | Overall width of the carrier tape                         |

| - [ | P1 | Pitch between successive cavity centers                   |

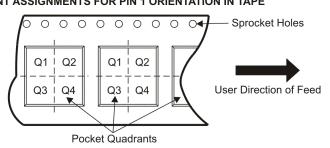

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |    |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|---------|---------|---------|------------|-----------|------------------|

| SN74LS191DR  | SOIC            | D                  | 16 | 2500 | 330.0                    | 16.4                     | 6.5     | 10.3    | 2.1     | 8.0        | 16.0      | Q1               |

| SN74LS191NSR | SO              | NS                 | 16 | 2000 | 330.0                    | 16.4                     | 8.2     | 10.5    | 2.5     | 12.0       | 16.0      | Q1               |

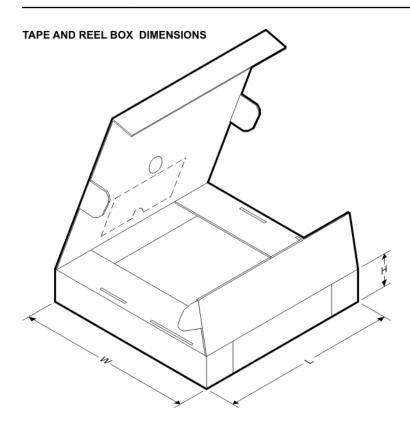

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| SN74LS191DR  | SOIC         | D               | 16   | 2500 | 333.2       | 345.9      | 28.6        |

| SN74LS191NSR | SO           | NS              | 16   | 2000 | 346.0       | 346.0      | 33.0        |

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

**Applications Products Amplifiers** amplifier.ti.com Audio www.ti.com/audio Data Converters Automotive www.ti.com/automotive dataconverter.ti.com DLP® Products Broadband www.dlp.com www.ti.com/broadband DSP Digital Control dsp.ti.com www.ti.com/digitalcontrol Clocks and Timers www.ti.com/clocks Medical www.ti.com/medical Military Interface www.ti.com/military interface.ti.com Optical Networking Logic logic.ti.com www.ti.com/opticalnetwork Power Mgmt power.ti.com Security www.ti.com/security Telephony Microcontrollers microcontroller.ti.com www.ti.com/telephony Video & Imaging www.ti-rfid.com www.ti.com/video RF/IF and ZigBee® Solutions www.ti.com/lprf Wireless www.ti.com/wireless

> Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2009, Texas Instruments Incorporated